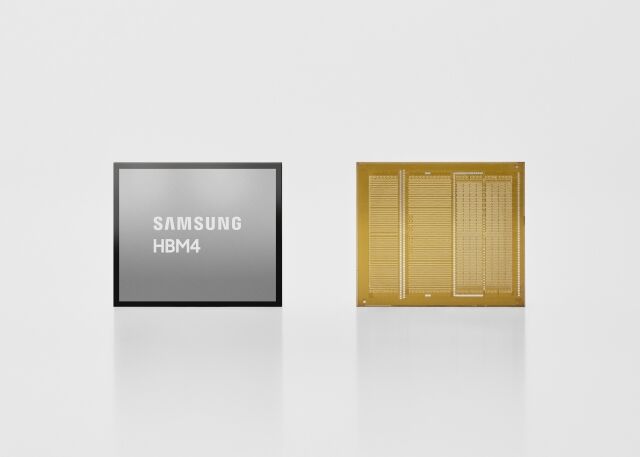

[마이데일리 = 윤진웅 기자] 삼성전자가 세계 최초로 6세대 고대역폭메모리(HBM) HBM4를 양산 출하하며 AI 반도체 시장 주도권 확보에 나섰다. 최선단 1c D램과 4나노 공정을 적용해 성능과 전력 효율을 동시에 끌어올려 경쟁력을 키웠다.

삼성전자는 12일 HBM4를 세계 최초로 양산 출하했다고 밝혔다. HBM4 개발 착수 단계부터 JEDEC 기준을 상회하는 성능 목표를 설정해 추진했으며, 이번 제품에는 10나노급 6세대 1c D램과 파운드리 4나노 공정을 적용했다. 재설계 없이 양산 초기부터 안정적인 수율과 업계 최고 수준의 성능을 확보했다는 설명이다.

황상준 삼성전자 메모리개발담당 부사장은 “기존 검증 공정을 적용하던 전례를 깨고 1c D램과 4나노 등 최선단 공정을 도입했다”며 “공정 경쟁력과 설계 개선을 통해 고객의 성능 상향 요구에 적기 대응할 수 있었다”고 강조했다.

HBM4는 JEDEC 업계 표준 8Gbps를 약 46% 상회하는 11.7Gbps 동작 속도를 안정적으로 확보했다. 이는 전작 HBM3E 최대 핀 속도 9.6Gbps 대비 약 1.22배 향상된 수치다. 최대 13Gbps까지 구현 가능하다. 단일 스택 기준 메모리 대역폭은 전작 대비 약 2.7배 향상된 최대 3.3TB/s로, 고객 요구 수준인 3.0TB/s를 넘어섰다.

용량은 12단 적층 기준 최대 36GB를 제공하며, 16단 적층 기술 적용 시 최대 48GB까지 확장할 계획이다.

전력 효율과 발열 개선도 병행했다. I/O 핀 수가 1024개에서 2048개로 확대됨에 따라 코어 다이에 저전력 설계를 적용하고, TSV 저전압 설계(1.1V→0.75V)와 전력 분배 네트워크(PDN) 최적화를 통해 전 세대 대비 에너지 효율을 약 40% 개선했다. 열 저항은 약 10%, 방열 특성은 약 30% 향상됐다.

삼성전자는 로직·메모리·파운드리·패키징을 아우르는 IDM 체제를 기반으로 원스톱 솔루션을 제공할 수 있는 점을 강점으로 내세웠다. 자체 파운드리 공정과 HBM 설계 간 DTCO 협업을 통해 품질과 수율을 동시에 확보하겠다는 전략이다.

회사는 2026년 HBM 매출이 2025년 대비 3배 이상 증가할 것으로 전망하고 생산 능력을 선제 확대하고 있다. 2028년부터 본격 가동될 평택사업장 2단지 5라인은 HBM 생산의 핵심 거점으로 활용될 예정이다.

차세대 제품도 준비 중이다. HBM4E는 2026년 하반기 샘플 출하를 목표로 개발하고 있으며, 고객 맞춤형 커스텀HBM은 2027년부터 순차 샘플링에 돌입할 계획이다. 삼성전자는 HBM4 양산 과정에서 확보한 1c 공정 기반 품질과 공급 안정성을 토대로 고부가 제품 전환을 가속화한다는 방침이다.

Copyright ⓒ 마이데일리 무단 전재 및 재배포 금지

--comment--

첫 번째 댓글을 작성해 보세요.

댓글 바로가기